4K2K ディスプレイグラフィックス用コネクタ – EMIの低減

目次:

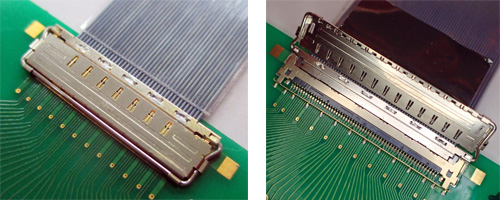

ソルダーテールのシールド処理による EMI の軽減

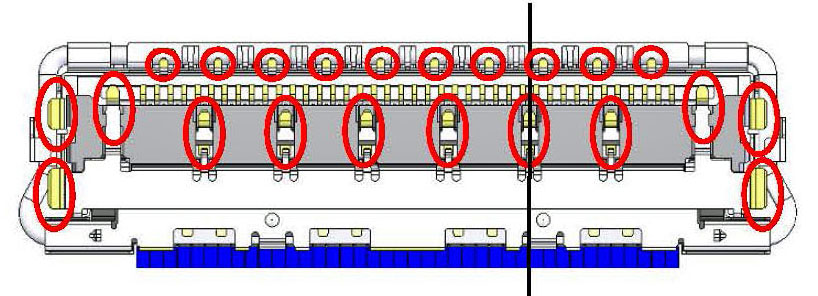

このディスプレイ グラフィックス用 コネクタのソルダーテールは、伝送速度が5.4 Gbpsである為、露出した状態ではナイキスト周波数 2.7 GHzのEMI を発生させ、多くの無線通信周波数帯に干渉します。そこで、シールドが必要となります。図 1に示したソルダ―テールを覆う一体型のシールドカバーがディスプレイ グラフィックス コネクタの設計に組み込まれたことにより、デバイス ソリューションにおいてこの機能を付加する追加措置 (金属テープを貼付する、金属製カバーを別途グラフィックス コネクタに追加するなど) は不要となりました。

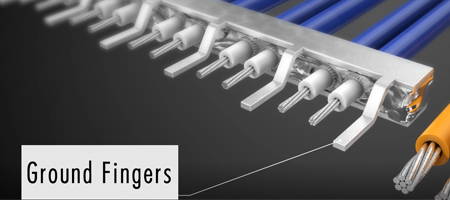

平衡接続における終端部のグランド

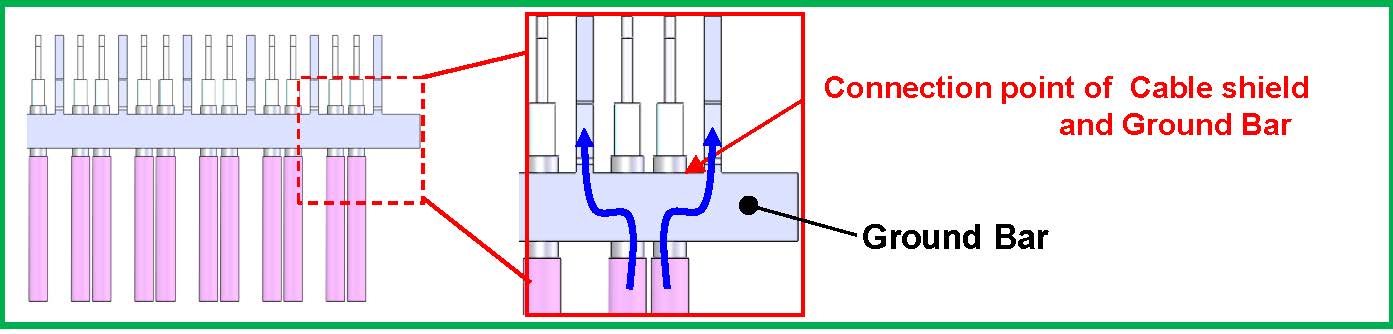

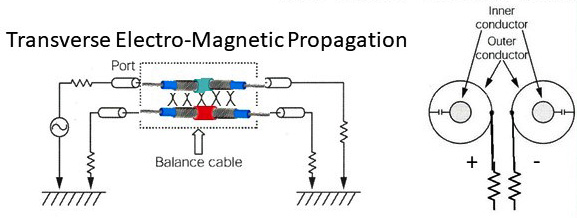

この高速伝送用グラフィックス コネクタでは、差動伝送方式で動作する同軸線の終端は、ファラデー ケージで覆われています。前処理済みの同軸線の外部シールドを上下2枚のグランド バーで半田付して、図2に示すように同軸線間の隙間(空隙)を完全に埋めることで頑丈なグランド バー構造を形成します。これによって、ケーブルが引っ張られた際、中心導体とコネクタのプラグ ハウジングの接続部における機械的張力が緩和されます。グランド フィンガーが、差動伝送方式で動作する各同軸線対間の隔壁となります。これによって、以下の図3に青い矢印で示した最短のグランド経路が実現します。

これらのグランド フィンガーにより、差動伝送方式で動作する同軸伝送線において平衡終端が実現するため、図4に示した信号のような差動データの高速伝送が可能となります。

終端が「不平衡」の場合、差動モードからコモン (同相) モードへの変換量 (Scd21: 横方向変換損 (TCTL) として知られるノイズ) が増大し、EMI が発生します。図5は、陽極の静電容量が陰極の静電容量を相殺する平衡終端を示したものです。優れたグランド バー構造であれば、終端におけるScd21は一般に約-25dBとなります。

終端部のシールド処理

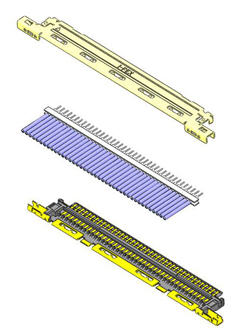

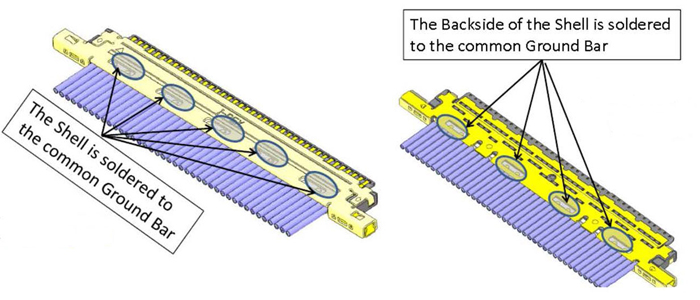

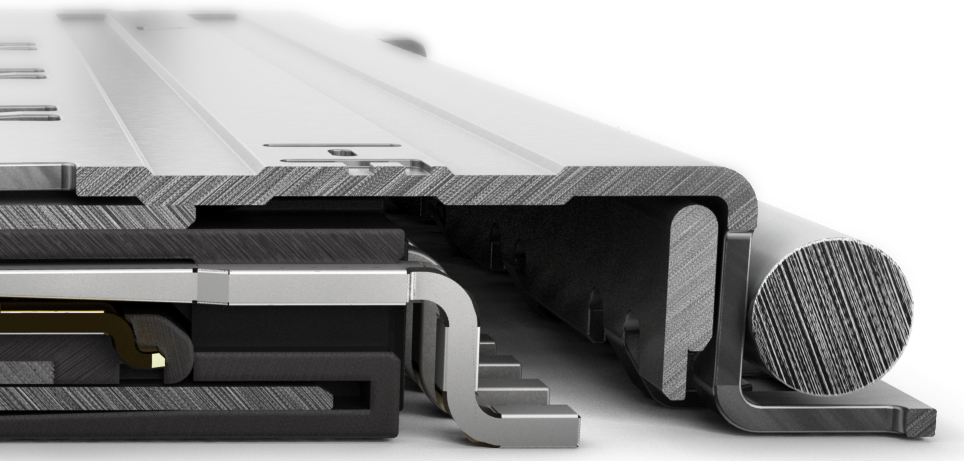

前処理済みのワイヤー アッセンブリをプラグ ハウジングに結合した後、同軸線の終端部の上に上部金属シェルを取り付けます。

続いて、プラグ コネクタ アセンブリの上下両方でシェルをグランド バーに半田付けします。

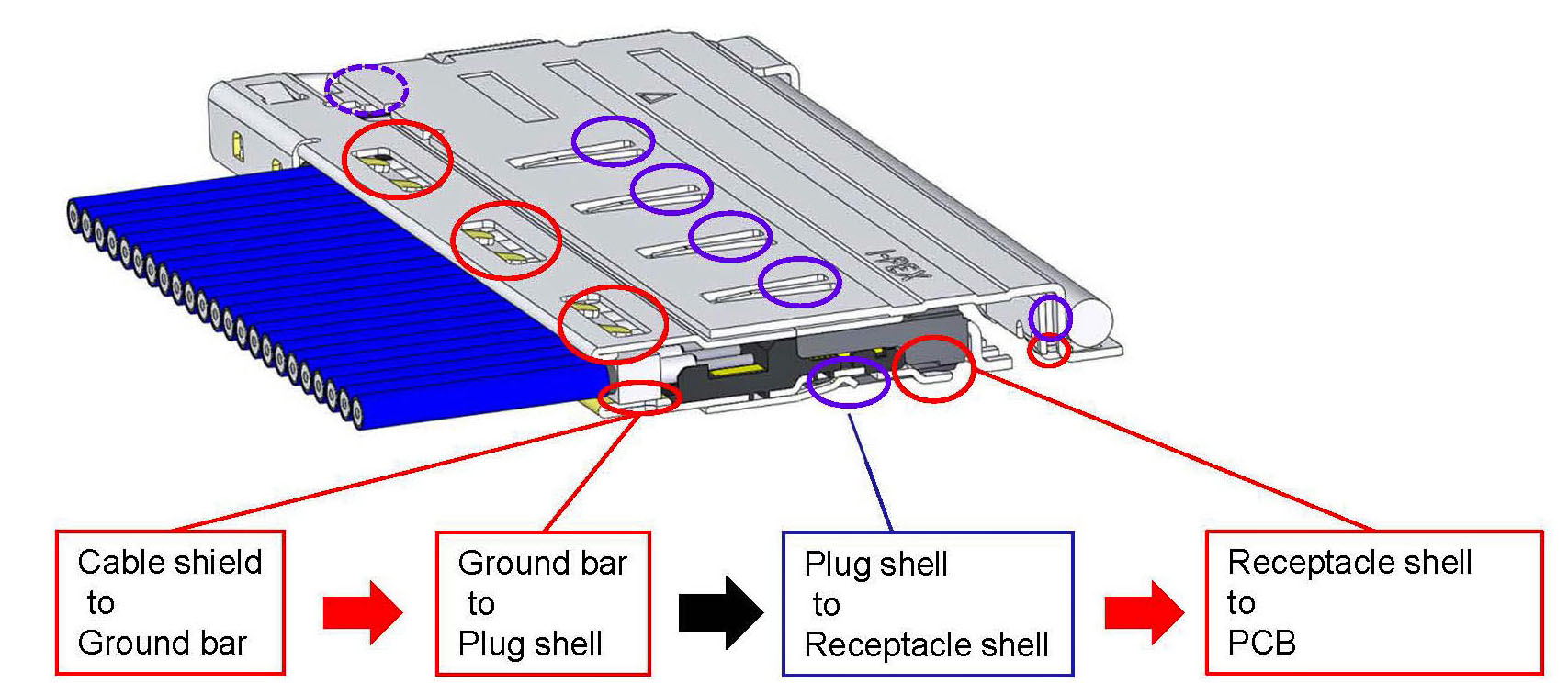

シールドのグランド経路は、同軸線シールドからコネクタ シェルを通じてグランド バー、さらにプラグ シェルへとつながっています。プラグシェルは図8のとおりレセプタクル シェルと接しており、図9に示したレセプタクル底部のグランド コンタクトの配置に沿って最短のグランド経路を通っています。グランド経路が短いことにより、高速での優れた信号伝達が可能となります。

遮蔽蓋/板とソルダー テールの間の隙間は、短絡が発生しうる部位と見なされていました。この設計(図 10)では、最低1.7 mmのクリアランスを絶対的に確保しています。

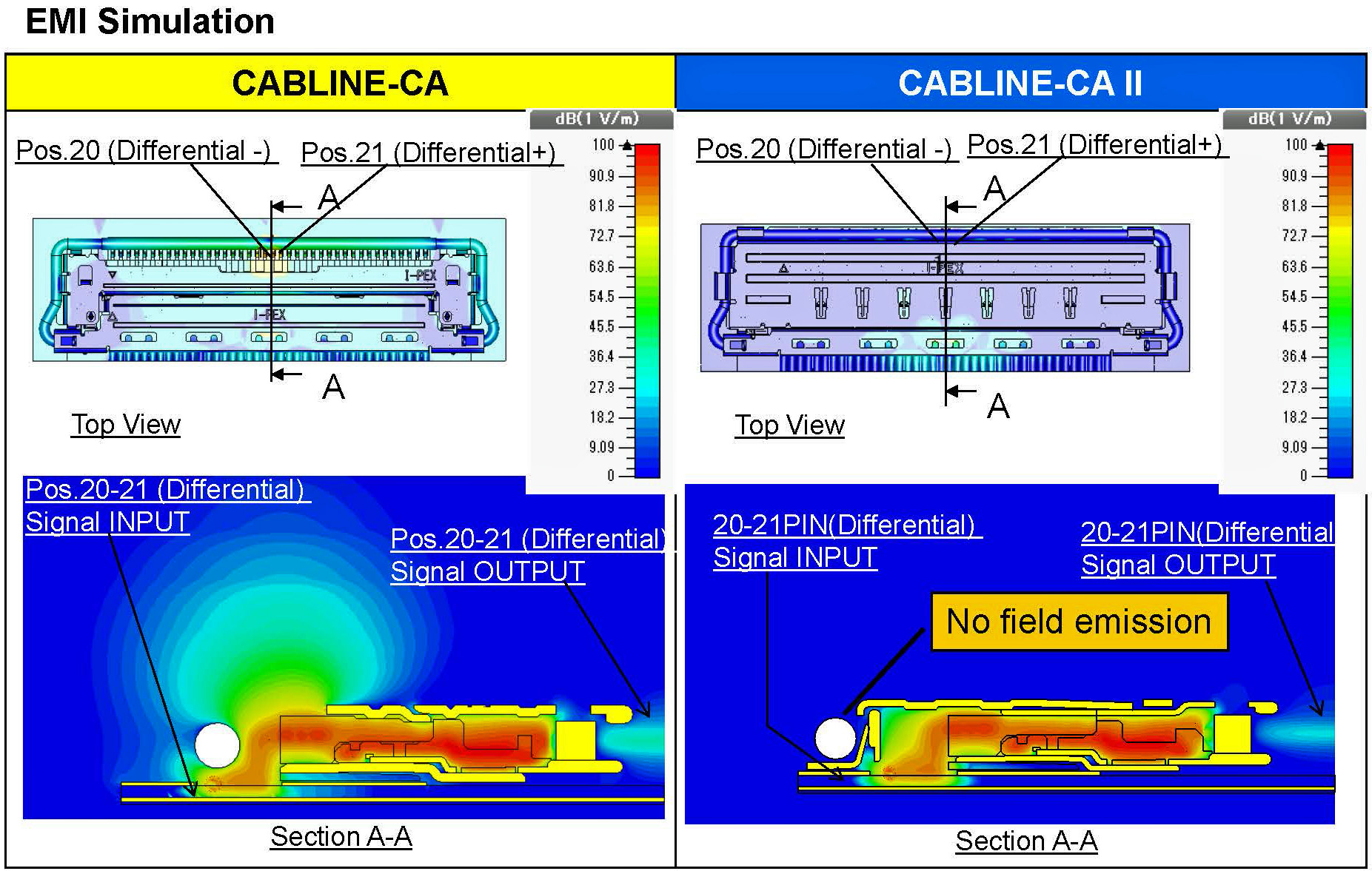

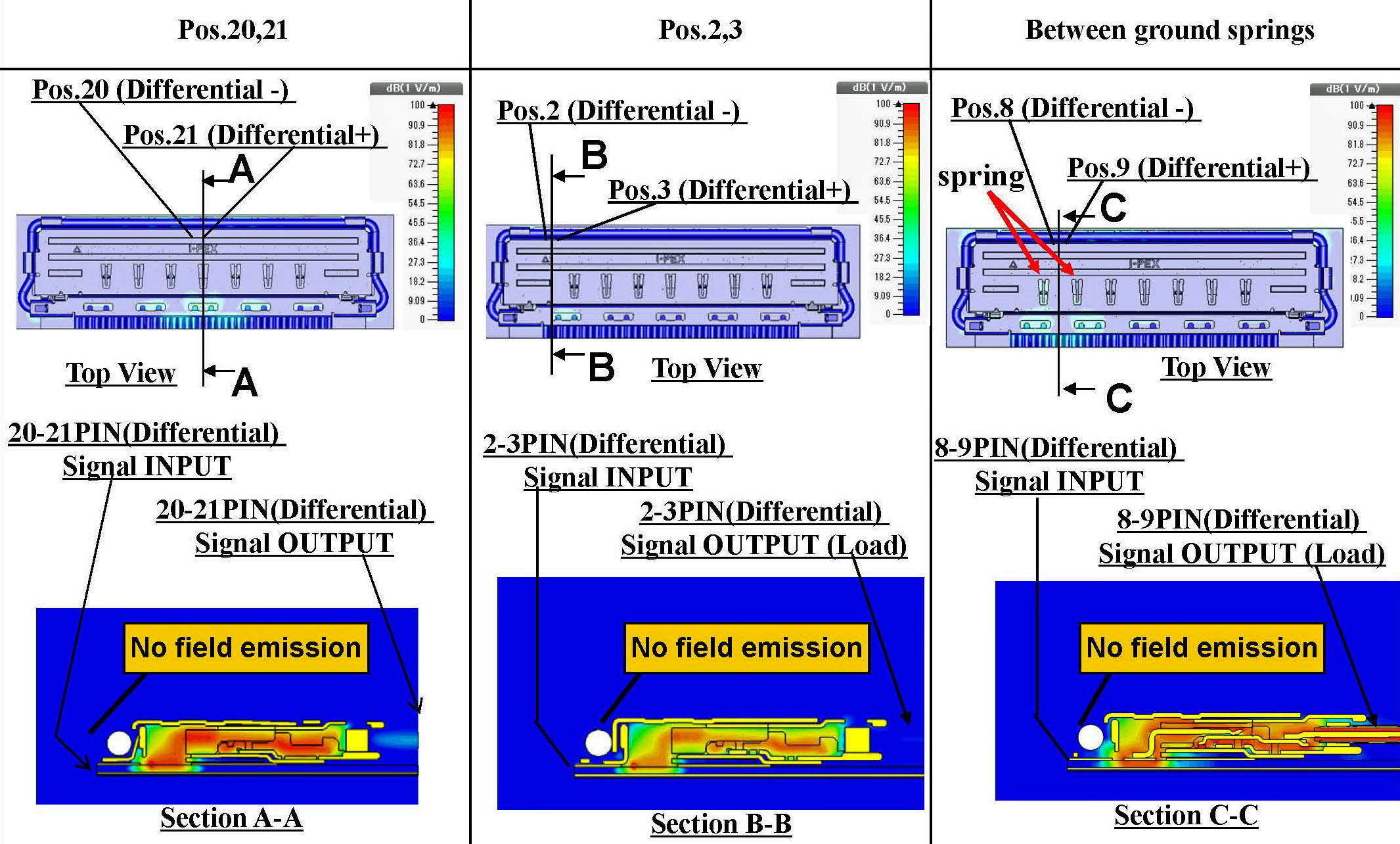

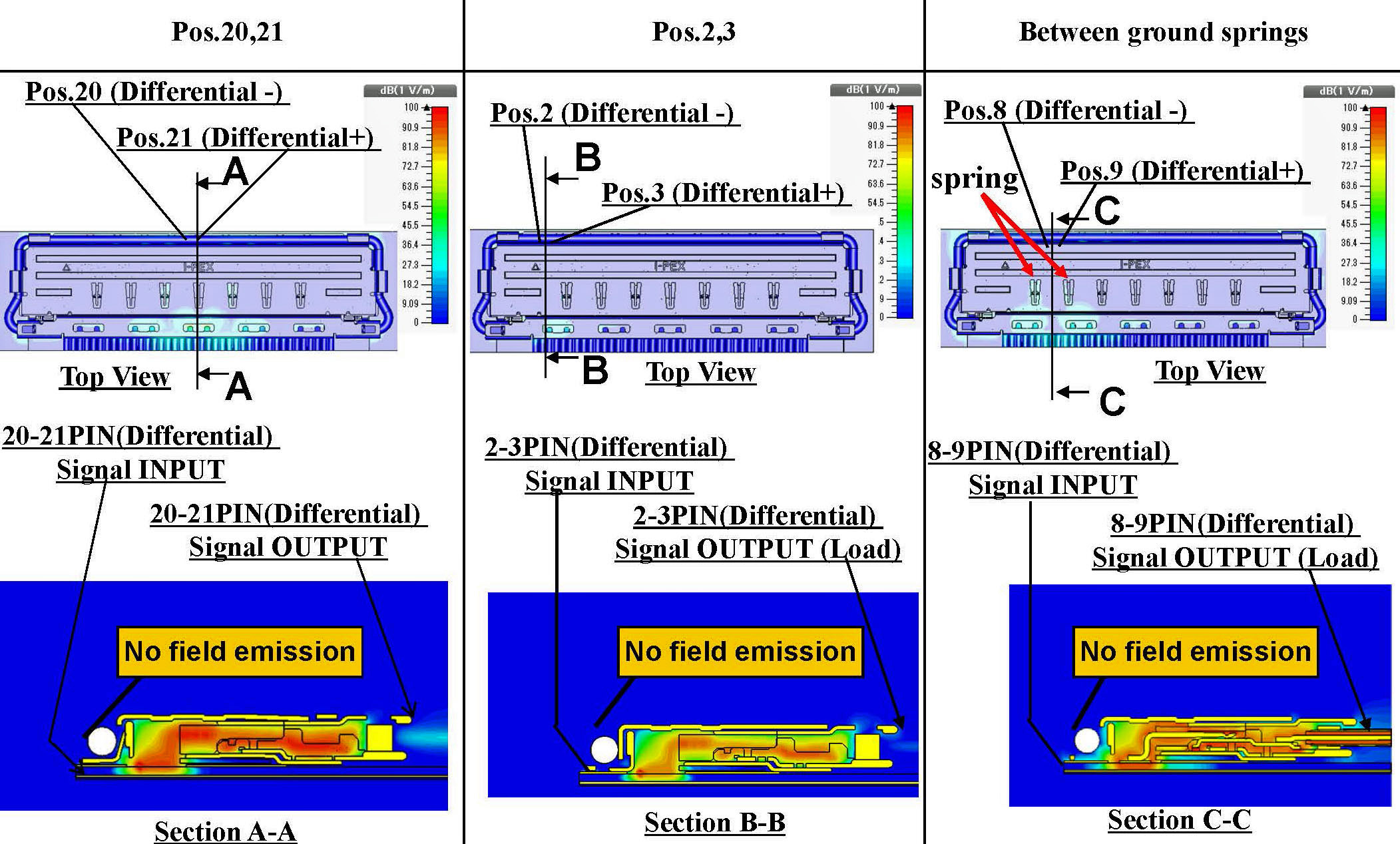

CST Microwave Studioを使用して図 11のとおり電界強度解析を実施し、ソルダー テール部にシールドがある場合とない場合で、このグラフィックス コネクタの電界放射を比較しました。

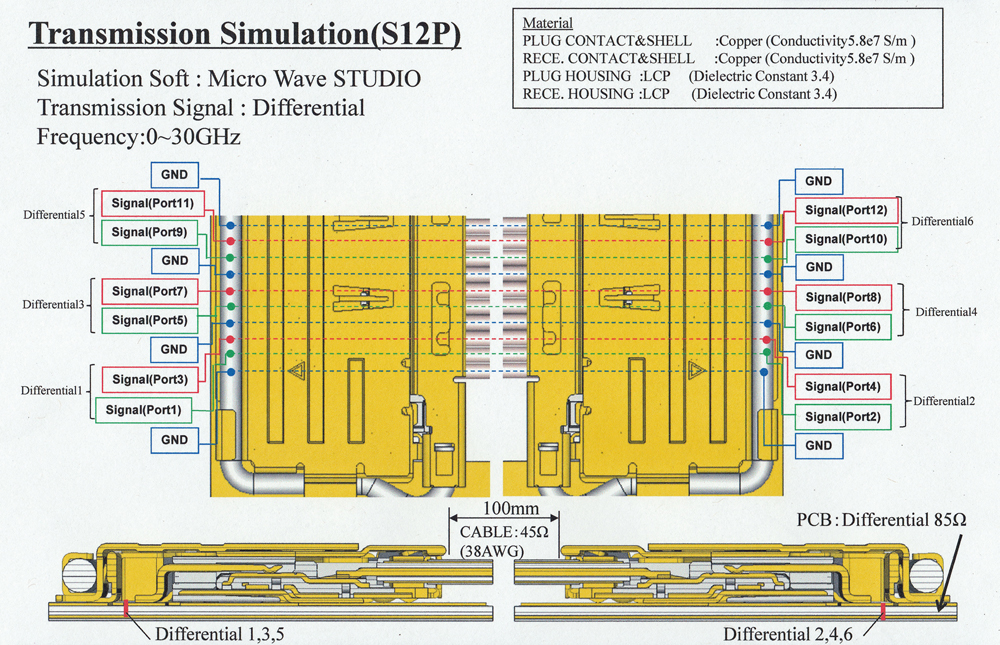

シミュレーションは3箇所のレーンで行いました。解析されたのは、一方の端に近いピン 2 と 3 の位置、およびコネクタ中央付近のピン 20 と 21、そして 3 か所目はピン 8 と 9 の近くにあるシールド カバーのグランド フィンガー間です。シミュレーションのセットアップにおいては、図 11 のとおり、GSSGSSGSS という伝送路配列を採用しています。

ソルダ―テールを覆う一体型のシールドをもつグラフィックス コネクタと、ソルダーテール シールド カバーが無い状態の同コネクタで、 20 GHz の高負荷信号を伝送した場合の電界強度の比較は、図12 のとおりです。

コネクタ上の3か所 (ピン 20~21、2~3、グランド スプリング間) における電界シミュレーションについては、周波数2.4 GHz(約5 Gbps) の場合を図13に、 5GHz (約10Gbps)の場合を図14 にて示しています。

このシミュレーションを見ると、ソルダー テールをシールドで覆った場合には、グラフィックス コネク タから電界は放射されないことがわかります。

データ伝送速度と周波数の関係は、「ナイキスト周波数」という用語で説明されます。5.4 Gbps (HBR2) の場合のナイキスト周波数は 2.7GHzであり、これは一部のLTE事業者の周波数帯と同じです。 2.7 GHz 前後のLTE アンテナ送受信部に近接している 場合、ソルダー テールがシールドされていないグラフィックス コネクタは、ナイキスト周波数約 2.7 GHz の電波を放射します。コネクタのソルダー テールか らの放射 (ナイキスト周波数) と、 2.7 GHz前後の LTEキャリア周波数の間に発生する干渉は、通信回線の障害の原因となります。 さて、EMI の問題は解決しましたので、次に、信号品位の性能解析を見てみましょう。時間領域で解析した特性インピーダンス プロファイルと散乱パラメータ (Sパラメータ) を使用して、挿入損失、反射減衰量、遠端クロストーク、近端クロストーク、および前述の差動モードからコモン モードへの変換特性 (Scd21) といったパラメータを周波数領域で解析し ます。図 11 に示した 3 つの差動レーンに対する解析では、共有可能なTouchstone形式の s12p ファイルが生成されます。

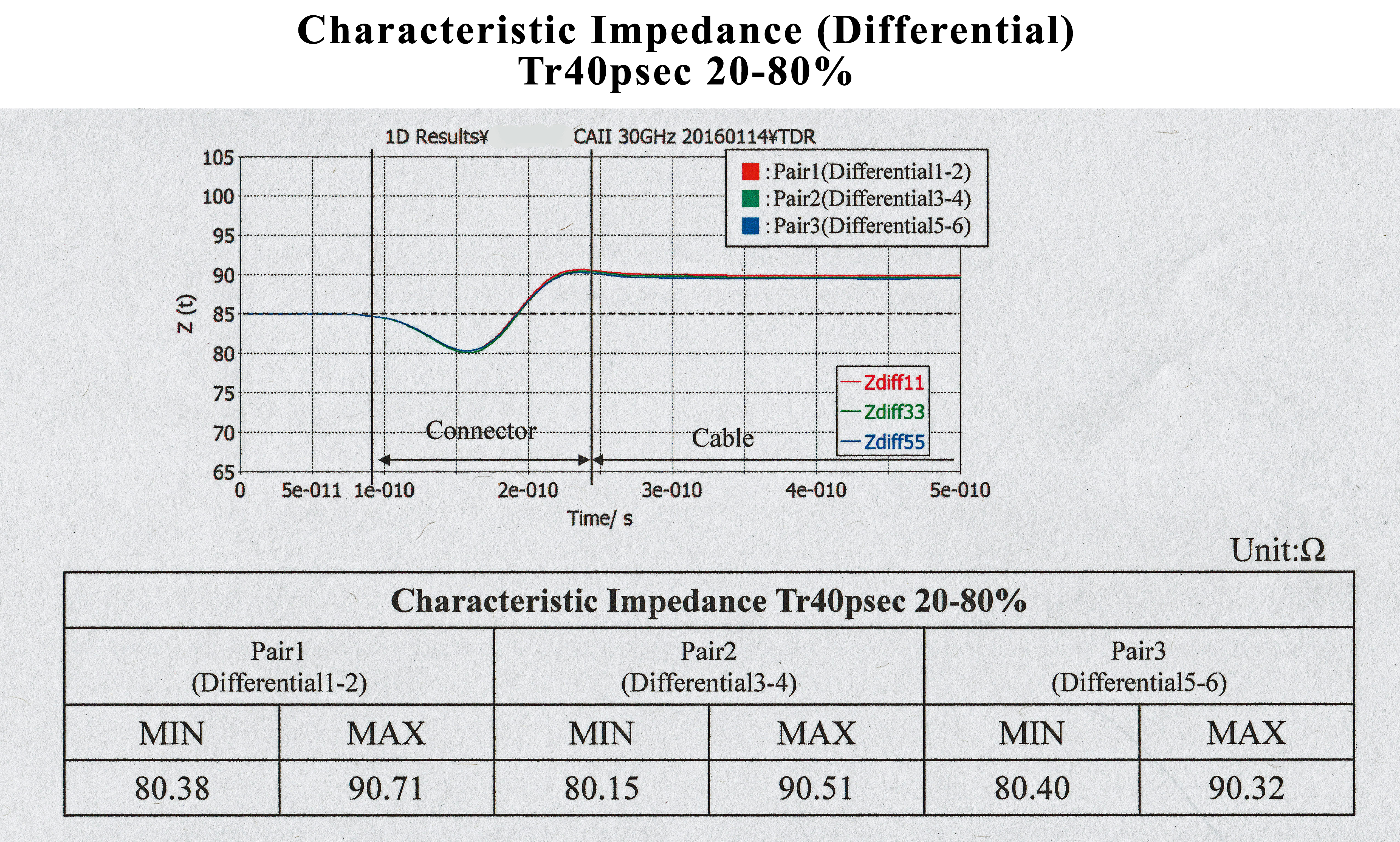

グラフィックス コネクタのインピーダンスの連続性

このグラフィックス コネクタでは、優れたグランド 構造により、インピーダンスの不連続性を最小限に抑えながら eDP HBR2 (5.4 Gbps) での差動信号伝送を実現できます。5.4Gbps というデータ伝送速度は一般に立ち上がり時間 Tr=64 ps (20%~80%) と同等とされますが、USB-IFがデータ伝送速度10 Gbps に対し Tr=40ps (20%~80%) を推奨していることを踏まえ、この性能 解析では図 15 に示すとおり Tr=40ps (20%~80%) を使用しました。

このコネクタにおける10 Gbps (5 GHz) でのインピーダンスの不連続性は、平均して約Δ10.2 オームです。 この結果は、同コネクタが優れた反射減衰量 (低反射) と優れたクロストーク特性 (高分離性) を有するこ とを示唆しています。伝送路のインピーダンス経路に大きなばらつき (不連続性) がある場合は、反射減衰量およびクロストーク特性に問題が見られます。 また、その場合、差動モードからコモン モードへの変換の悪化が予測されます。

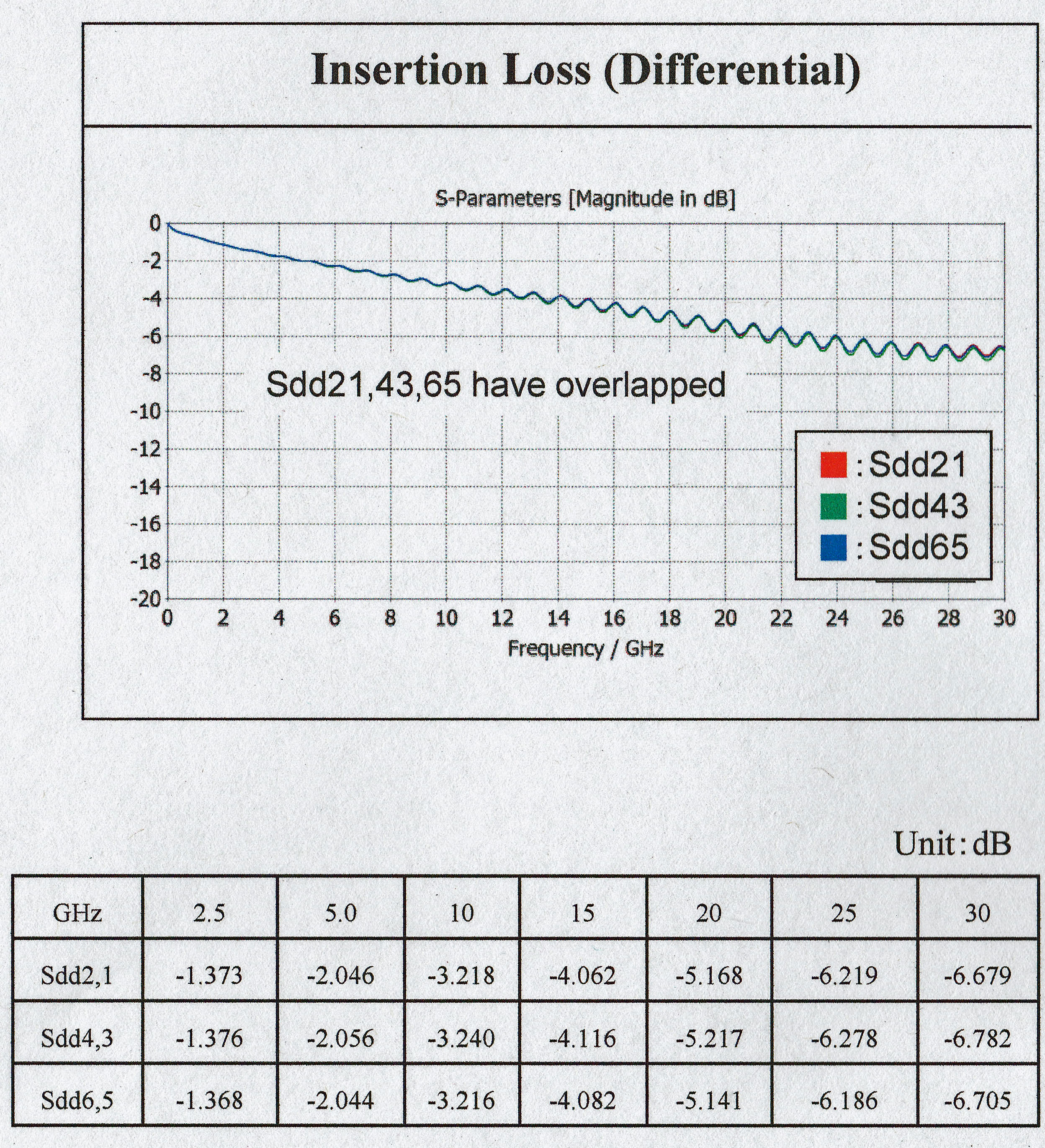

挿入損失と反射減衰量 (s12p)

図16には、長さ100 mmの終端処理済みケーブル (45 オームに制御されたインピーダンスを有する細線同軸線 AWG38 を使用) における挿入損失を示しています。たとえば 5 Gbps (2.5 GHz) の場合、挿入損失は 2dB 未満です。

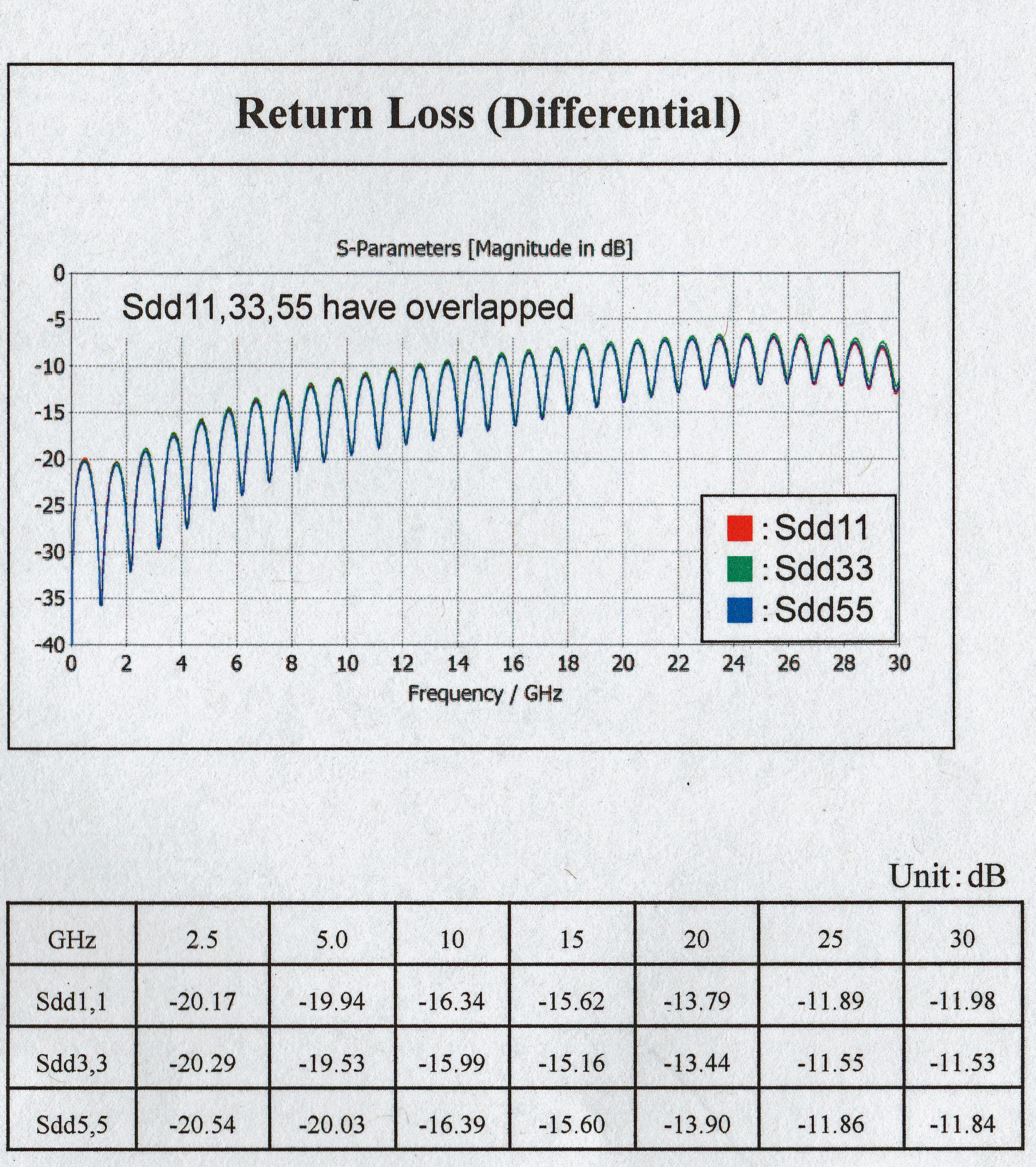

図 17 に示した長さ100 mmのケーブルにおける反射減衰量は、-10dBよりも悪化した (12 GHz 超) 時点で許容不可能となります。ケーブル長が短いほど反射経路が短くなるため、反射減衰量が劣ります。

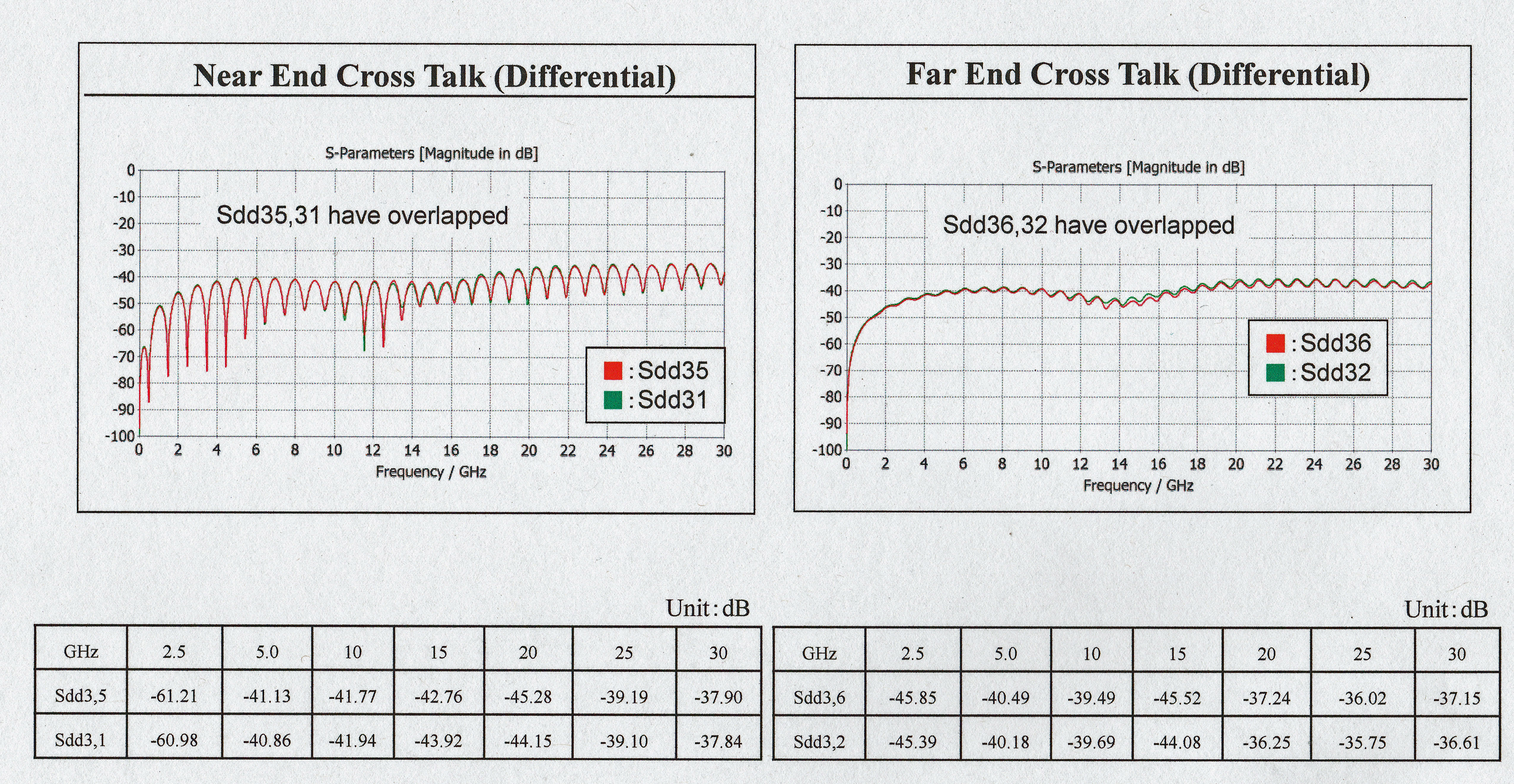

図 18 に示すこのケーブルにおけるクロストーク特性のシミュレーションでも、良好な結果が出ています。

ソルダ―テールを覆う一体型シールドロックカバーを搭載したeDP グラフィックス用コネクタのデザインは、データ伝送速度が上昇し続ける中で、より高解像度のディスプレイ アッセンブリをサポートできるという点が特徴的です。

参考文献

1. I-PEX, “IER-001-07244-00,” Simulation Transmission, January 15, 2016

2. I-PEX, “IER-001-06877-00,” Grounding Bar Design, May 29, 2015

3. David E. Bockelman and William R. Eisenstadt, “Combined Differential and Common-Mode Scattering Parameters” IEEE

Vol.43, No.7, July 1955