ウエハー製品 (KRYSTAL® Wafer)

お客様の成膜装置で単結晶成膜をご希望の場合、ZrO2バッファーや下部電極KRYSTAL® Waferを使用した単結晶成膜に関するアドバイスなども行っております。

KRYSTAL® Waferとは

優れた単結晶圧電薄膜の成膜技術により開発したZrO2 Buffer(下地層)を使用することで、上に成膜する様々な圧電材料を単結晶化し、高性能化することができる優れた圧電MEMS用ウエハーです。

KRYSTAL® Wafer の製品タイプ

- 対応基板材質: Si基板、SOI基板

- 標準対応基板サイズ: 6インチ、8インチ

-

ZrO2 バッファー基板(ZrO2)

金属であるジルコニウム(Zr)の酸化物である二酸化ジルコニウムはジルコニアとも呼ばれ、高い融点をもつ物質として知られていますが、結晶構造としては、空間群P4₂/nmcに分類されるDitetragonal dipyramidal構造をとります。このピラミッド構造は上層の材料の格子定数に合わせるように変形し、上層材料の単結晶化に寄与しています。これがKRYSTAL® Waferの単結晶技術のキーテクノロジーとなっています。

金属であるジルコニウム(Zr)の酸化物である二酸化ジルコニウムはジルコニアとも呼ばれ、高い融点をもつ物質として知られていますが、結晶構造としては、空間群P4₂/nmcに分類されるDitetragonal dipyramidal構造をとります。このピラミッド構造は上層の材料の格子定数に合わせるように変形し、上層材料の単結晶化に寄与しています。これがKRYSTAL® Waferの単結晶技術のキーテクノロジーとなっています。

-

下部電極Pt基板(Pt/ZrO2)

抵抗が低く、薄膜化が容易なため、圧電素子の成膜時に電極としてよく使用されています。お客様からのご指定により、ZrO₂上にPt膜を成膜したものを提供いたします。

抵抗が低く、薄膜化が容易なため、圧電素子の成膜時に電極としてよく使用されています。お客様からのご指定により、ZrO₂上にPt膜を成膜したものを提供いたします。

-

下部電極SRO/Pt基板(SRO/Pt/ZrO2)

ルテニウム酸ストロンチウムSRO(SrRuO₃)は強磁性体金属酸化物の一種でRuddlesden-popper型化合物です。結晶構造はペロブスカイト型構造をとり、Pt膜上に成膜することによって、膜安定性を向上させます。KRYSTAL® Waferの標準仕様の下地電極膜に使用されています。

ルテニウム酸ストロンチウムSRO(SrRuO₃)は強磁性体金属酸化物の一種でRuddlesden-popper型化合物です。結晶構造はペロブスカイト型構造をとり、Pt膜上に成膜することによって、膜安定性を向上させます。KRYSTAL® Waferの標準仕様の下地電極膜に使用されています。

-

単結晶PZT基板

逆圧電効果利用向けの設計。高いd定数と耐電圧性を持ちながら、低い誘電率を実現した、バランスを取った仕様のPZTです。

逆圧電効果利用向けの設計。高いd定数と耐電圧性を持ちながら、低い誘電率を実現した、バランスを取った仕様のPZTです。

-

上部電極付単結晶PZT基板

単結晶PZT膜の上に上部電極としてSRO+Pt膜を成膜して納品いたします。

単結晶PZT膜の上に上部電極としてSRO+Pt膜を成膜して納品いたします。

*KRYSTAL® Waferの単結晶PZT薄膜に上部電極を成膜する場合、Pt(白金)/SRO(ルテニウム酸ストロンチウム)の膜構成を標準的に提案しています。

開発技術

-

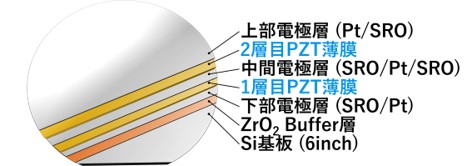

積層単結晶PZT(2層PZT)基板

KRYSTAL® Wafer の優れた単結晶成膜技術を応用し、単結晶薄膜PZTを積層成膜。 圧電特性が向上し、高出力・高精度なアクチュエーター駆動を実現可能。 更に詳しく

KRYSTAL® Wafer の優れた単結晶成膜技術を応用し、単結晶薄膜PZTを積層成膜。 圧電特性が向上し、高出力・高精度なアクチュエーター駆動を実現可能。 更に詳しく

(現在、6インチウエハーにて開発中)

-

非鉛系(鉛フリー)圧電薄膜基板

PZT膜は優れた特性を示し、様々な用途に利用されていますが、その一方で材料に微量の鉛成分が含まれているため、近年の環境や健康への影響の観点から使用が制限される場合があります。PZT膜と同等以上の特性を実現する非鉛系圧電素材の単結晶化にも取り組んでおります。